Version 2.0

April 1997 Edition Part Number 340007B-01

© Copyright 1991, 1997 National Instruments Corporation. All Rights Reserved.

### Internet Support

support@natinst.com

E-mail: info@natinst.com

FTP Site: ftp.natinst.com

Web Address: http://www.natinst.com

### **Bulletin Board Support**

BBS United States: (512) 794-5422 BBS United Kingdom: 01635 551422 BBS France: 01 48 65 15 59

**Fax-on-Demand Support** (512) 418-1111

Telephone Support (U.S.)

Tel: (512) 795-8248 Fax: (512) 794-5678

International Offices

Australia 03 9879 5166, Austria 0662 45 79 90 0, Belgium 02 757 00 20, Canada (Ontario) 905 785 0085, Canada (Québec) 514 694 8521, Denmark 45 76 26 00, Finland 09 527 2321, France 01 48 14 24 24, Germany 089 741 31 30, Hong Kong 2645 3186, Israel 03 5734815, Italy 02 413091, Japan 03 5472 2970, Korea 02 596 7456, Mexico 5 520 2635, Netherlands 0348 433466, Norway 32 84 84 00, Singapore 2265886, Spain 91 640 0085, Sweden 08 730 49 70, Switzerland 056 200 51 51, Taiwan 02 377 1200, U.K. 01635 523545

National Instruments Corporate Headquarters

6504 Bridge Point Parkway Austin, TX 78730-5039 Tel: (512) 794-0100

# **Important Information**

#### Warranty

National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it. EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

#### Trademarks

Product and company names listed are trademarks or trade names of their respective companies.

#### WARNING REGARDING MEDICAL AND CLINICAL USE OF NATIONAL INSTRUMENTS PRODUCTS

National Instruments products are not designed with components and testing intended to ensure a level of reliability suitable for use in treatment and diagnosis of humans. Applications of National Instruments products involving medical or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the part of the user or application designer. Any use or application of National Instruments products for or involving medical or clinical treatment must be performed by properly trained and qualified medical personnel, and all traditional medical safeguards, equipment, and procedures that are appropriate in the particular situation to prevent serious injury or death should always continue to be used when National Instruments products are being used. National Instruments products are NOT intended to be a substitute for any form of established process, procedure, or equipment used to monitor or safeguard human health and safety in medical or clinical treatment.

## 1. Introduction

| 1.1 Scope                                  | 1-1 |

|--------------------------------------------|-----|

| 1.2 Objectives                             | 1-2 |

| 1.3 Introduction to MXI-2                  | 1-2 |

| 1.4 Conventions Used in This Specification | 1-3 |

# 2. Physical Characteristics

| 2.1 System Description     | 2-1 |

|----------------------------|-----|

| 2.2 Device Connector       |     |

| 2.3 Cable Assemblies       | 2-4 |

| 2.3.1 System Configuration | 2-6 |

| 2.3.2 Cable                |     |

| 2.3.3 Cable Connector      | 2-8 |

| 2.4 Termination            | 2-9 |

| 2.5 Electrical Description |     |

| L                          |     |

# 3. Signals and Timing

| 3.1 Address/Data                 |  |

|----------------------------------|--|

| 3.1.1 Address Broadcast          |  |

| 3.1.1.1 Address Lines            |  |

| 3.1.1.2 Address Modifier Lines   |  |

| 3.1.1.3 CONVERT* Line            |  |

| 3.1.1.4 WR* Line                 |  |

| 3.1.2 Data Transfers             |  |

| 3.1.2.1 Basic Data Transfers     |  |

| 3.1.2.2 Block Transfers          |  |

| 3.1.2.3 Synchronous-Burst Cycles |  |

| 3.1.2.3.1 Initiation             |  |

|                                  |  |

| 3.1.2.3.2 Data Transfer                | 3-22 |

|----------------------------------------|------|

| 3.1.2.3.3 Termination                  | 3-25 |

| 3.1.2.4 Indivisible Transfers          | 3-33 |

| 3.1.2.5 Priority-Selection Cycles      | 3-36 |

| 3.1.2.6 RETRY and BERR* Acknowledgment | 3-40 |

| 3.2 Arbitration                        | 3-44 |

| 3.3 Interrupt                          | 3-49 |

| 3.4 Timing                             | 3-50 |

| 3.5 Utility                            | 3-50 |

# 4. Device-Dependent Considerations

| 4.1 Deadlock                  | 4-1 |

|-------------------------------|-----|

| 4.2 Byte Swapping             |     |

| 4.3 Memory Management         | 4-4 |

| 4.4 Resource Locking          | 4-4 |

| 4.5 Interface Registers       |     |

| 4.6 Power Up/Down             | 4-6 |

| 4.6.1 System Controller       |     |

| 4.6.2 Terminators             | 4-7 |

| 4.6.3 Daisy-Chain Propagation | 4-7 |

|                               |     |

# Appendix

## Glossary

## Index

## Figures

| Figure 2-1. | MXIbus System Connection Example                 |  |

|-------------|--------------------------------------------------|--|

| Figure 2-2. | Device Connector Pin (Front View)                |  |

| Figure 2-3. | Multidrop Cable Assembly                         |  |

| Figure 2-4. | MXIbus System Configuration Scheme               |  |

| Figure 2-5. | Single-Ended Signal Termination Network Examples |  |

| Figure 2-6. | Differential Signal Termination Network Examples |  |

|             |                                                  |  |

| Figure 3-1. | Basic Write Cycle Timing                         |  |

| Basic Read Cycle Timing                                            | 3-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

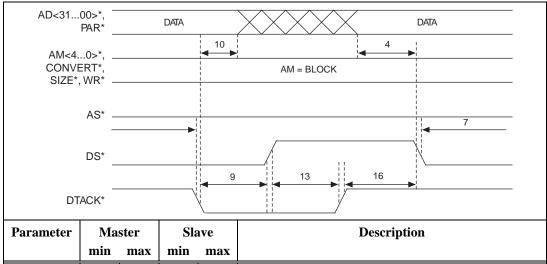

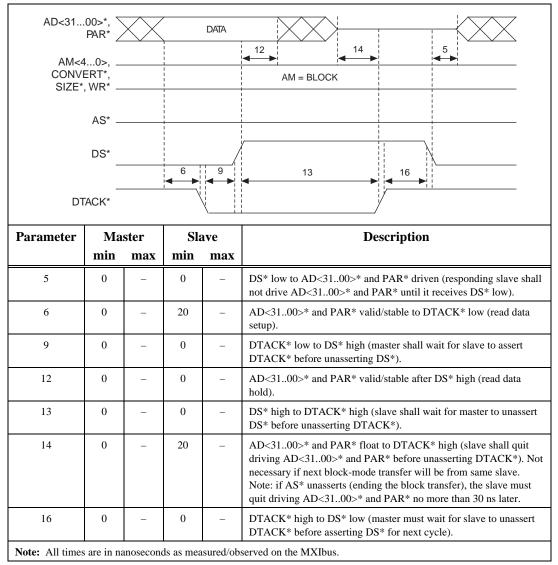

| Block-Read Cycle Timing                                            | 3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

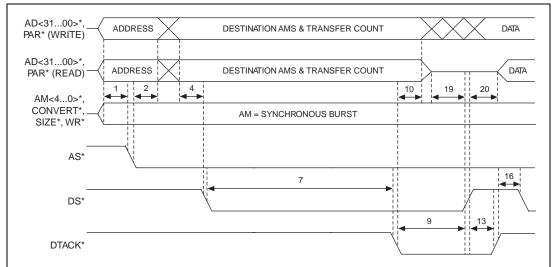

| Synchronous-Burst Initiation Transfer Timing                       | 3-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

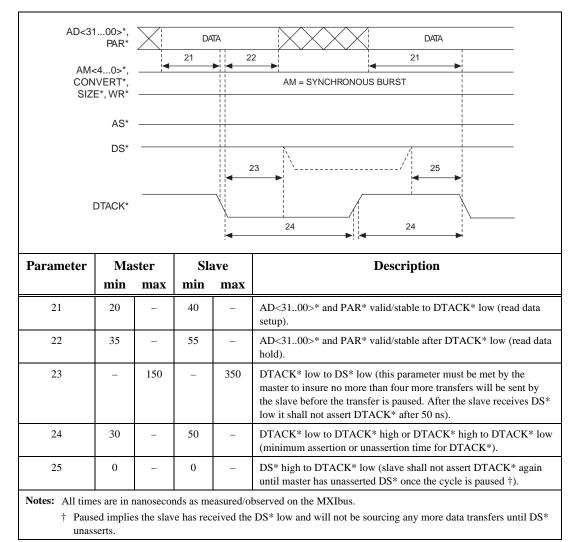

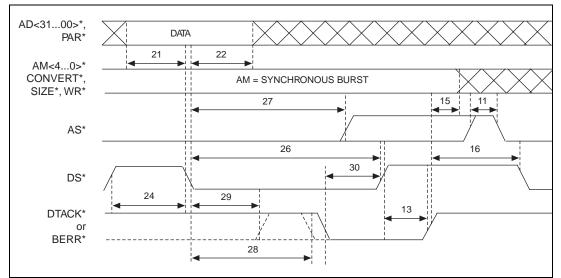

| Synchronous Burst-Write Transfer Timing                            | 3-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Synchronous Burst-Read Transfer Timing                             | 3-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

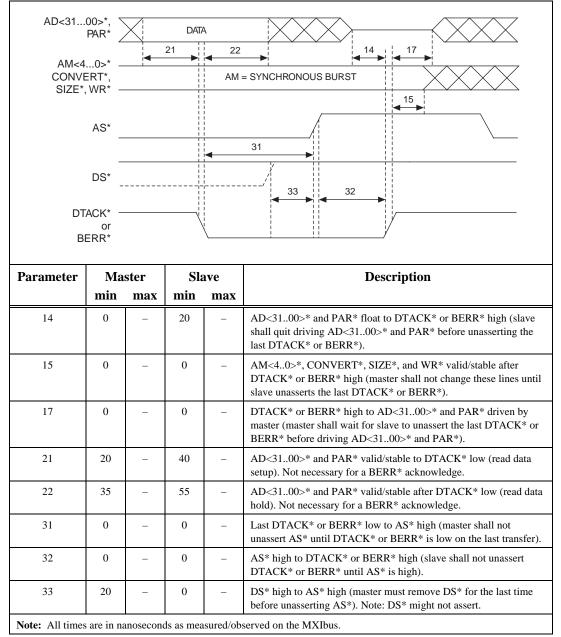

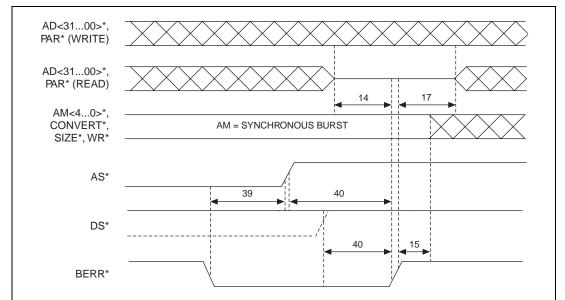

| Synchronous Burst-Write Cycle Termination Timing                   | 3-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Synchronous Burst-Read Cycle Termination Timing                    | 3-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

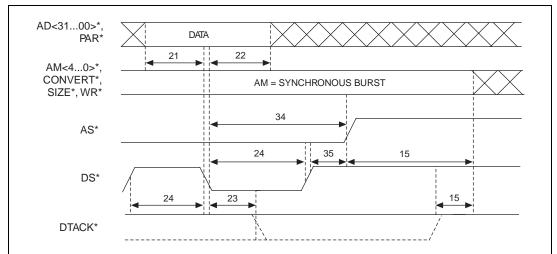

| Prematurely Master-Terminated Synchronous Burst-Write Cycle Timing | 3-30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Prematurely Master-Terminated Synchronous Burst-Read Cycle Timing  | 3-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

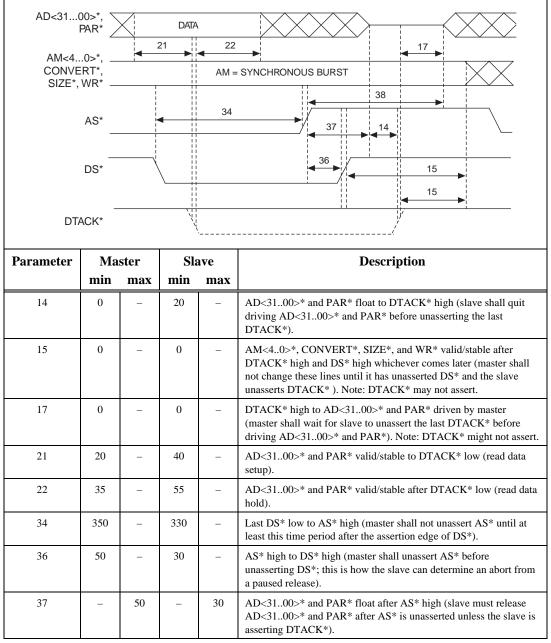

| Prematurely Slave-Terminated Synchronous-Burst Cycle Timing        | 3-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Indivisible Cycle Timing                                           | 3-35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Priority-Selection Cycle Timing                                    | 3-39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RETRY and BERR* Acknowledgment                                     | 3-43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Arbitration Requester Timing                                       | 3-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

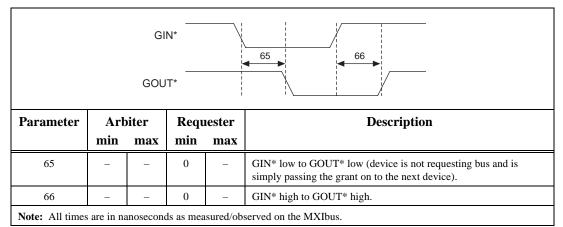

| Grant In/Grant Out Daisy-Chain Timing                              | 3-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

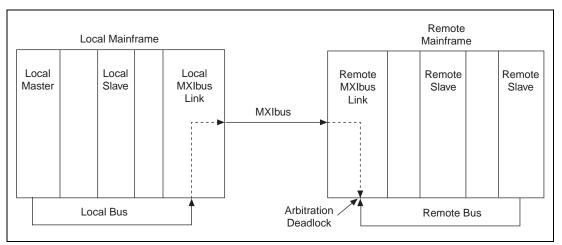

| Data Transfer Bus Arbitration Deadlock                             | 4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                    | Basic Read Cycle Timing<br>Block-Write Cycle Timing<br>Block-Read Cycle Timing<br>Synchronous-Burst Initiation Transfer Timing<br>Synchronous Burst-Write Transfer Timing<br>Synchronous Burst-Read Transfer Timing<br>Synchronous Burst-Read Transfer Timing<br>Synchronous Burst-Read Cycle Termination Timing<br>Synchronous Burst-Read Cycle Termination Timing<br>Prematurely Master-Terminated Synchronous Burst-Write Cycle Timing<br>Prematurely Master-Terminated Synchronous Burst-Read Cycle Timing<br>Prematurely Slave-Terminated Synchronous-Burst Cycle Timing<br>Priority-Selection Cycle Timing<br>RETRY and BERR* Acknowledgment<br>Arbitration Requester Timing<br>Data Transfer Bus Arbitration Deadlock |

## Tables

| Table 2-1. | Device Connector Pin Assignments                  | 2-3  |

|------------|---------------------------------------------------|------|

| Table 2-2. | System Configuration Truth Table                  | 2-8  |

| Table 2-3. | Logical/Electrical Signal Levels                  | 2-11 |

| Table 3-1. | Signal Groupings                                  | 3-1  |

| Table 3-2. | Address Modifier Codes                            | 3-5  |

| Table 3-3. | Byte Addressing                                   | 3-7  |

| Table 3-4. | Data Transfer Types                               |      |

| Table 3-5. | Basic Data Transfer Cycle Address Modifier Codes  |      |

| Table 3-6. | Block Transfer Address Modifier Codes             |      |

| Table 3-7. | Synchronous-Burst Transfer Address Modifier Codes |      |

# Introduction

### 1.1 Scope

The Multisystem eXtension Interface bus (MXIbus) is a multidrop parallel bus architecture designed for high-speed communication between devices. The MXIbus is a general-purpose gateway that you can use to communicate between two or more devices, such as personal computers, workstation computers, VXIbus mainframes, VMEbus-based computers, stand-alone instruments, or modular instruments.

The MXIbus links together multiple devices by mapping together sections of their address spaces. This address map connection makes remote MXIbus devices appear as if they are local memory resources of other MXIbus devices. For example, an IBM PC AT computer with an AT bus-to-MXIbus interface can control multiple VXIbus mainframes equipped with MXIbus-to-VXIbus interfaces. The VXIbus mainframes with their plug-in instrument modules then appear to the PC AT as if they were plugged directly into the backplane of the PC AT. When the PC AT performs a read or write to a memory location that maps to one of the remote instrument modules, the AT-MXI interface translates the PC AT bus cycle into a MXIbus bus cycle to the remote VXI-MXI interface, which further translates the MXIbus cycle into a VXIbus cycle to reach the particular memory location in the VXIbus mainframe.

The MXIbus architecture is a very high-performance link between devices because it maps actual bus cycles on one device to bus cycles on another device. Because it is a multidrop, multimaster architecture with a full 32-bit multiplexed address and data pathway, multiple 8-, 16-, or 32-bit MXIbus devices can dynamically communicate with each other and control each other's resources at very high speeds. Accessing remote devices is straightforward because all MXIbus device memory is written and/or read through memory mapping.

## 1.2 Objectives

This specification defines the mechanical, electrical, and functional requirements for the MXIbus. The system objectives of the MXIbus specification are as follows:

- To specify the system characteristics that allow communication between devices that are physically located in different mainframes, enclosures, or chassis

- To specify the electrical and mechanical system characteristics required to design devices that will reliably and unambiguously communicate with other devices interfaced to the MXIbus

- To specify the physical layer protocols that define the interaction between devices and the MXIbus

- To define terminology that describes the MXIbus system and the devices that are interfaced to it

A glossary of terms used in this specification is at the back of this document. Section 2 describes the physical characteristics of MXIbus devices and systems. These include the MXIbus cables, connectors, terminators, and electrical specifications. There are 71 active MXIbus signals that are used to transfer data between MXIbus devices, arbitrate between contending devices, and perform interrupt, trigger, and error-detection functions. Some of these signals have certain timing relationships that ensure signal integrity, described in Section 3. Section 4 contains device-specific information to consider when designing a MXIbus interface.

### 1.3 Introduction to MXI-2

MXI-2 is the second generation of the MXIbus. MXI-2 expands the number of signals on a standard MXI cable by including all VME interrupts, VXI triggers, CLK10, and all of the VMEbus utility bus signals. Because MXI-2 incorporates all of these signals into a single connector, the triggers, interrupts, and utility signals can extend not only between VXI/VME mainframes, but also to external devices/computers. Thus in a MXI-2 system, CPU interface boards can perform as if they were plugged directly into the VXI/VME backplane.

In addition, MXI-2 boosts data throughput performance past previousgeneration MXIbus products by defining new high-performance protocols. MXI-2 is a superset of MXI. All accesses that MXIbus devices initiate will work with MXI-2 devices. However, MXI-2 defines synchronous MXI block data transfers that surpass previous block data throughput benchmarks. The new synchronous MXI block protocol increases MXI-2 throughput to a maximum of 33 MB/s between two MXI-2 devices.

## 1.4 Conventions Used in This Specification

The following conventions are used in this specification:

| <>           | Angle brackets containing numbers separated by an ellipsis represent a range of values associated with a bit or signal name (for example, BDIO<30>).                                                                             |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bold italic  | Bold italic text denotes a note, caution, or warning.                                                                                                                                                                            |

| italic       | Italic text denotes emphasis, a cross reference, or an introduction to a key concept.                                                                                                                                            |

| signal names | Signal names appear in all uppercase letters.                                                                                                                                                                                    |

| numbers      | All numbers are in decimal unless otherwise specified in a suffix to the number. An $-h$ after a number indicates that the number is in hexadecimal format. A $-b$ after a number indicates that the number is in binary format. |

# **Physical Characteristics**

This section describes the physical characteristics of MXIbus devices and systems, and the cables, connectors, connector signal assignments, cable termination, and electrical specifications needed to implement the MXIbus.

## 2.1 System Description

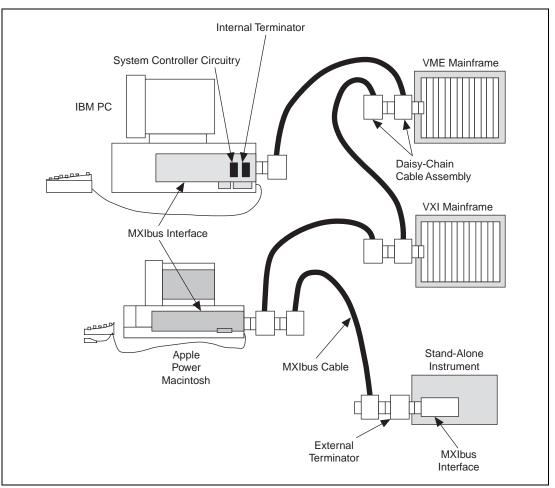

A MXIbus system consists of a series of connections between devices via shielded cables. Multiple MXIbus devices are connected together in a linear fashion using cables with common signals. Star configurations are not allowed.

Both ends of the MXIbus are terminated. Terminators may be either stand-alone external devices or embedded inside a device. Embedded terminators must be removable or have the ability to be disabled. All signals except GIN\* (grant in), GOUT\* (grant out), MXISC\* (MXIbus System Controller), ENDDEV (MXIbus End Device), AUXPWR (auxiliary power), and TERMPWR (termination power) are common (that is, bused) between MXIbus devices. Figure 2-1 illustrates an example MXIbus system.

Figure 2-1. MXIbus System Connection Example

The first MXIbus device in the daisy-chain is referred to as the *MXIbus System Controller*. The MXIbus System Controller contains the MXIbus arbiter functional module, the MXIbus priority-select cycle daisy-chain driver, and the MXIbus timeout monitor functional module. Implementation of MXIbus System Controller functionality is optional for a MXIbus device. Each MXIbus device that contains MXIbus System Controller functionality must have a method for defeating the System Controller circuitry. There must be one and only one device in a MXIbus system that functions as the MXIbus System Controller.

### 2.2 Device Connector

MXIbus specifies the use of shielded, 144-position, high-density connectors for MXIbus devices. MXIbus device connectors consist of four rows of receptacle contacts with adjacent contacts 1.27 mm (0.05 in.) apart, and are physically keyed to ensure proper connection. Device connectors are shielded and connected to the unit's chassis ground to help reduce electromagnetic radiation interference (EMI) and to provide electrostatic discharge (ESD) protection. The metal shell and retaining screw sockets of the MXIbus device connector must make electrical contact with the unit's chassis ground. The device connector has threaded socket inserts that accept the locking screws of the cable assembly connector.

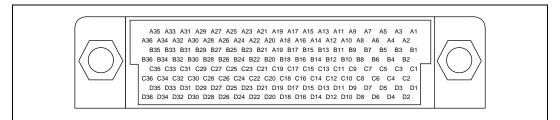

The MXIbus signals must be assigned to the device connector as shown in Figure 2-2. The signal descriptions and timing relationships are given in Section 3.

Figure 2-2. Device Connector Pin (Front View)

| Pin | Signal Name |

|-----|-------------|-----|-------------|-----|-------------|-----|-------------|

| A1  | AD(31)*     | B1  | AD(14)*     | C1  | AM(4)*      | D1  | BUSY*       |

| A2  | GND         | B2  | GND         | C2  | GND         | D2  | GND         |

| A3  | AD(30)*     | B3  | AD(13)*     | C3  | AM(3)*      | D3  | IRQ(1)*     |

| A4  | GND         | B4  | GND         | C4  | GND         | D4  | GND         |

| A5  | AD(29)*     | B5  | AD(12)*     | C5  | AM(2)*      | D5  | IRQ(2)*     |

| A6  | GND         | B6  | GND         | C6  | GND         | D6  | GND         |

| A7  | AD(28)*     | B7  | AD(11)*     | C7  | AM(1)*      | D7  | IRQ(3)*     |

| A8  | GND         | B8  | GND         | C8  | GND         | D8  | GND         |

| A9  | AD(27)*     | B9  | AD(10)*     | C9  | AM(0)*      | D9  | IRQ(4)*     |

Table 2-1. Device Connector Pin Assignments

(Continues)

| Pin | Signal Name |

|-----|-------------|-----|-------------|-----|-------------|-----|-------------|

| A10 | GND         | B10 | GND         | C10 | GND         | D10 | GND         |

| A11 | AD(26)*     | B11 | AD(9)*      | C11 | WR*         | D11 | IRQ(5)*     |

| A12 | GND         | B12 | GND         | C12 | GND         | D12 | GND         |

| A13 | AD(25)*     | B13 | AD(8)*      | C13 | SIZE*       | D13 | IRQ(6)*     |

| A14 | GND         | B14 | GND         | C14 | GND         | D14 | GND         |

| A15 | AD(24)*     | B15 | AD(7)*      | C15 | BTODIS*     | D15 | IRQ(7)*     |

| A16 | GND         | B16 | GND         | C16 | GND         | D16 | GND         |

| A17 | AD(23)*     | B17 | AD(6)*      | C17 | ACFAIL*     | D17 | TRG(0)+     |

| A18 | GND         | B18 | GND         | C18 | GND         | D18 | TRG(0)-     |

| A19 | AD(22)*     | B19 | AD(5)*      | C19 | SYSRESET*   | D19 | TRG(1)+     |

| A20 | GND         | B20 | GND         | C20 | GND         | D20 | TRG(1)-     |

| A21 | AD(21)*     | B21 | AD(4)*      | C21 | SYSFAIL*    | D21 | TRG(2)+     |

| A22 | GND         | B22 | GND         | C22 | GND         | D22 | TRG(2)-     |

| A23 | AD(20)*     | B23 | AD(3)*      | C23 | BERR*       | D23 | TRG(3)+     |

| A24 | GND         | B24 | GND         | C24 | GND         | D24 | TRG(3)-     |

| A25 | AD(19)*     | B25 | AD(2)*      | C25 | DTACK*      | D25 | TRG(4)+     |

| A26 | GND         | B26 | GND         | C26 | GND         | D26 | TRG(4)-     |

| A27 | AD(18)*     | B27 | AD(1)*      | C27 | DS*         | D27 | TRG(5)+     |

| A28 | GND         | B28 | GND         | C28 | GND         | D28 | TRG(5)-     |

| A29 | AD(17)*     | B29 | AD(0)*      | C29 | AS*         | D29 | TRG(6)+     |

| A30 | GND         | B30 | GND         | C30 | GND         | D30 | TRG(6)-     |

| A31 | AD(16)*     | B31 | CONVERT*    | C31 | BREQ*       | D31 | TRG(7)+     |

| A32 | GND         | B32 | GND         | C32 | GND         | D32 | TRG(7)-     |

| A33 | AD(15)*     | B33 | PAR*        | C33 | GIN*        | D33 | CLK10+      |

| A34 | GND         | B34 | GND         | C34 | GND         | D34 | CLK10-      |

| A35 | AUXPWR      | B35 | TERMPWR     | C35 | GOUT*       | D35 | MXISC*      |

| A36 | AUXPWR      | B36 | TERMPWR     | C36 | GND         | D36 | ENDDEV      |

Table 2-1. Device Connector Pin Assignments (Continued)

## 2.3 Cable Assemblies

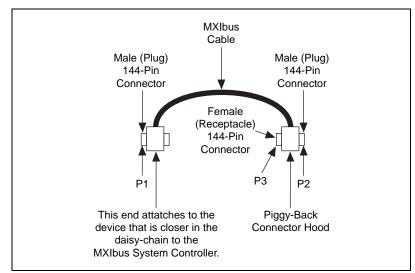

Cable assemblies connect MXIbus devices. MXIbus cable assemblies may be point-to-point, in which two devices are connected, or can be multidrop, whereby two or more devices are connected. Using multidrop cable assemblies, new devices are added to the system in a linear configuration using the cable's back-to-back connector arrangement, which is similar to the scheme used by the IEEE-488 (GPIB). One cable end contains a single male plug, and the other cable end contains both a male plug and a female receptacle. A diagram of a multidrop MXIbus cable assembly is shown in Figure 2-3.

Figure 2-3. Multidrop Cable Assembly

Point-to-point cable assemblies have only two male cable connectors, one on each cable end. All of the signal wires in the point-to-point cable assembly are bused point-to-point except for MXISC\*, ENDDEV, AUXPWR, TERMPWR, GIN\*, and GOUT\*. MXISC\* and ENDDEV are discussed later in this section. AUXPWR and TERMPWR are available only on the device connector; there are no connections in the cable. The GIN\* and GOUT\* signals are wired as follows:

| Signal Name | Connected To  |

|-------------|---------------|

| P1 GIN*     | No connection |

| P1 GOUT*    | P2 GIN*       |

| P2 GOUT*    | No connection |

All of the signal wires in the multidrop cable assembly are bused between all three connectors except for MXISC\*, ENDDEV, AUXPWR, TERMPWR, GIN\*, and GOUT\*. MXISC\* and ENDDEV are discussed later in this section. AUXPWR and TERMPWR are bused between P2 and P3, so that external terminators and other devices that make use of these power sources can be placed either on P3 or between P2 and the MXIbus device. P1 of the cable has no connection to AUXPWR and TERMPWR. The GIN\* and GOUT\* signals are wired as follows:

| Signal Name | Connected To  |

|-------------|---------------|

| P1 GIN*     | No connection |

| P1 GOUT*    | P2 GIN*       |

| P2 GOUT*    | P3 GOUT*      |

| P3 GIN*     | No connection |

Because MXIbus cables must properly propagate the GIN\*-to-GOUT\* daisy-chain signals, the cables are naturally polarized and must be properly connected for the system to function. The P1 connector end of the cable assembly must be attached to the device that is closer in the daisy-chain to the MXIbus System Controller. A point-to-point cable can be used as the last cable section in a MXIbus system since P3 of a multidrop cable would not be used in this position.

## 2.3.1 System Configuration

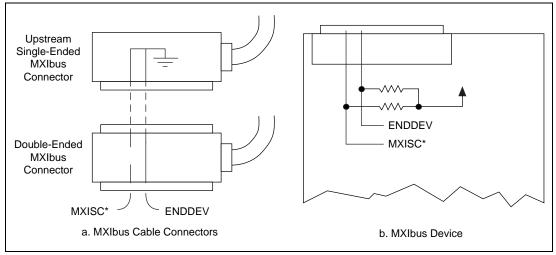

The two MXIbus signals MXISC\* and ENDDEV are used to aid in system configuration. The cable and connector configurations determine the logic level of these signals. A device that receives MXISC\* low will automatically assume MXIbus System Controller functions. It will also terminate the MXIbus. A device that receives ENDDEV high recognizes that it is the last device in the MXIbus daisy chain and will terminate the MXIbus.

Figure 2-4 shows the mechanism for implementing these signals. The single-ended connector shown should be the end of the cable electrically closest to the MXIbus System Controller (the upstream end). This is always true for a MXI cable with a single-ended connector on one end and a double-ended connector on the other end. A MXI cable with single connectors on each end is polarized, meaning that the upstream end, while physically similar to the downstream end, is not electrically the same and must be marked so that a user will install the cable with the upstream end closest to the MXIbus System Controller. The double-ended connector is always on the downstream end of the cable (farthest from the MXI System Controller).

Figure 2-4. MXIbus System Configuration Scheme

Every MXIbus device that uses the MXISC\* and/or ENDDEV signals must have pull-up resistors as shown in Figure 2-4.

The upstream single-ended connector pulls both MXISC\* and ENDDEV low. Because only a single-ended connector can connect to the MXIbus System Controller, the MXIbus System Controller will receive both signals low and thus terminate the MXIbus and assume System Controller functions.

The double-ended connector passes ENDDEV through from one side of the connector to the other. MXISC\* is not passed through the connector (neither signal is bused on the cable). A device in the middle of the MXIbus daisy chain has a dual-ended connector attached to it with the upstream end of a cable attached to the back of the dual-ended connector. That device will receive ENDDEV low and MXISC\* high, so it will neither terminate the MXIbus nor assume System Controller functions.

The last device in the MXIbus daisy chain will have either a doubleended connector or a downstream single-ended connector attached to it. Neither the downstream single-ended connector nor the double-ended connector pull MXISC\* and ENDDEV low. The downstream singleended connector does not need to connect to the two signals at all. Because the end device, by definition, has only a single cable attached to it (no piggy-backing of cables as with a middle device), no connector can be attached that will pull MXISC\* and ENDDEV low. The device will receive MXISC\* and ENDDEV both high and then terminate the MXIbus. It will not assume MXI System Controller functions.

Table 2-2 describes the function of a MXIbus device given the state of the MXISC\* and ENDDEV signals at its MXIbus connector.

| MXISC* | ENDDEV | MXIbus System<br>Controller? | Terminate MXI? |

|--------|--------|------------------------------|----------------|

| Low    | Х      | Yes                          | Yes            |

| High   | Low    | No                           | No             |

| High   | High   | No                           | Yes            |

Table 2-2. System Configuration Truth Table

### 2.3.2 Cable

Raw MXIbus cable requires 69 twisted wire pairs. An ideal impedance match with cable terminators implies a cable characteristic impedance of 120  $\Omega$  (single-ended).

Total cable length in a MXIbus system is limited to 20 m. Individual cable length between two MXIbus devices can be any length between 1 and 20 m.

### 2.3.3 Cable Connector

MXIbus cable connectors must be shielded, 144-position, high-density, plug and receptacle connectors. These connectors mate with the MXIbus device connectors and, optionally, with additional MXIbus cable connectors. The cable shield must be connected to the metal shell and retaining screws of all cable connectors. The metal shell and retaining screws of the cable connectors must provide electrical contact with the device's chassis ground through the device's mating connector shell and retaining screw sockets. Each cable connector must be fitted with a pair of captive locking screws. A retaining ring, or equivalent, must be used to retain the lock screw as a captive element.

All signal wires in the MXIbus cable must be connected to the proper pins of each connector in the cable assembly. The ground wire of each twisted pair must be connected to the ground pin adjacent to the corresponding signal pin.

## 2.4 Termination

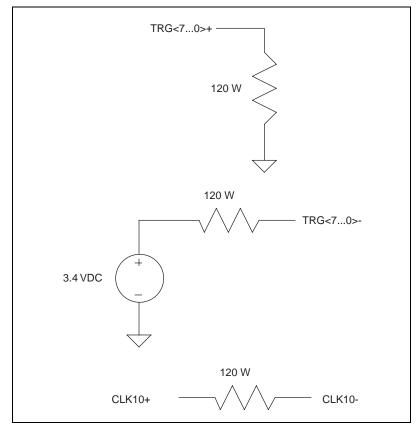

Termination networks must be positioned at the first and last MXIbus devices in the daisy-chain to minimize reflections due to impedance discontinuities at the ends of the cables, and also to bias the signal lines to a false state when they are not driven true. Each signal line must be terminated at both ends of the daisy-chain. The differential signals  $CLK10\pm$  and  $TRG<7..0>\pm$  must be terminated differently than the single-ended MXIbus signals.

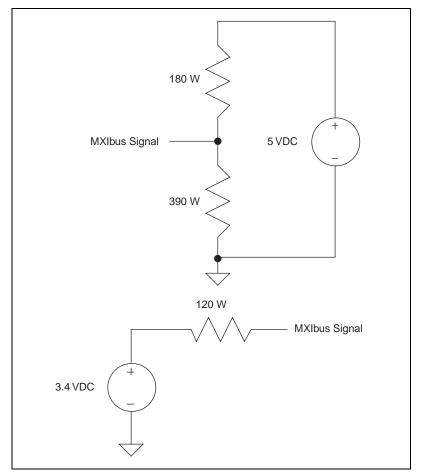

Example termination circuits for the single-ended signals are shown in Figure 2-5. The open-circuit termination voltage must be +3.4 V  $\pm$  5%, and the impedance of the termination must be 120  $\Omega \pm$  5%.

Figure 2-5. Single-Ended Signal Termination Network Examples

An example termination circuit for the differential signals is shown in Figure 2-6. The open-circuit termination voltage for the TRG<7..0>+ signals must be 0 V  $\pm$  5%, and the impedance of the termination must be 120  $\Omega \pm$  5%. The open-circuit termination voltage for the TRG<7..0>- signals must be +3.4 V  $\pm$  5%, and the impedance of the termination must be 120  $\Omega \pm$  5%. This termination scheme biases the trigger signals so that they are in the false state when not driven. The CLK10 $\pm$  signal does not need to be biased to a false state when not driven, so the example shows a simpler termination scheme for it.

Figure 2-6. Differential Signal Termination Network Examples

MXIbus termination may be provided using terminators that are external to the MXIbus devices in the system. MXIbus devices may also provide for optional internal termination. In addition, a MXIbus device can follow the automatic end-device detection scheme described earlier in this section to determine whether its internal termination circuit should be enabled. In any event, MXIbus terminators must be located within the maximum stub length dimension given in Section 2.5.

External terminators may provide their own power source, or they may use the termination power supplied by the TERMPWR pin of the device connector. TERMPWR support is optional for a device, but if supported, TERMPWR must provide 3.4 VDC  $\pm$  5% at a minimum of 2.5 A. It is recommended that MXIbus devices supply TERMPWR to the connector through protection circuitry that prevents the backflow of power to the MXIbus device, and excessive current draw from the TERMPWR pins.

The termination circuitry for the GIN\* and GOUT\* signals requires special attention because they are true daisy-chain signals, connected in a point-to-point fashion from device to device. The GIN\* signal can be received by a device, processed, and, optionally, retransmitted on the device's GOUT\* signal or, in the case of a MXIbus device that does not use the GIN\*-to-GOUT\* daisy-chain, the GIN\* input can be directly connected to the GOUT\* output with no logic connection. If the GIN\* and GOUT\* signals are connected to active logic on a MXIbus device, they must be terminated on that device, regardless of its position within the MXIbus daisy-chain. If the GIN\* and GOUT\* signals are connected to device, the terminated on that device is at one of the ends of the MXIbus daisy-chain.

### 2.5 Electrical Description

The relationship between the logical states and the electrical voltage level present on the MXIbus signal lines is shown in Table 2-3.

| Logical State | Electrical Level                                     |  |  |

|---------------|------------------------------------------------------|--|--|

| 0 False state | Corresponds to $\ge +2.0$ V<br>Called high level (H) |  |  |

| 1 True state  | Corresponds to ≤ +0.8 V<br>Called low level (L)      |  |  |

Table 2-3. Logical/Electrical Signal Levels

In general, the rise and fall times of signals on a bus are the result of a complex set of interactions involving the impedance of the cables, the termination network, the total length of the signal lines, the source impedance of the drivers, and the capacitive loading of the signal lines.

The MXIbus specification requires that all MXIbus devices use specific transceivers to guarantee reliable interoperability.

All MXIbus signals except MXISC\*, ENDDEV, and the differential signals CLK10 $\pm$  and TRG<7..0> $\pm$  must be driven and received by trapezoidal transceivers of a type equivalent to the National Semiconductor DS3662 or DS3862. The differential signals must be driven and received by differential transceivers of a type equivalent to the Texas Instruments SN75ALS176A. MXISC\* and ENDDEV can be received with any appropriate receiver for the MXIbus device. Each MXIbus signal must be subjected to no more than one transceiver load per MXIbus device. No more than eight devices (that is, eight transceiver loads) may be connected to the MXIbus at any one time.

Trapezoidal transceivers are used to reduce noise and crosstalk in the MXIbus transmission system. These transceivers have open-collector drivers that generate precise trapezoidal waveforms with typical rise and fall times of approximately 9 ns. The trapezoidal shape, due to the constant rise and fall times, reduces noise coupling (crosstalk) to adjacent lines. The receivers use a lowpass filter to remove noise in conjunction with a high-speed comparator, which recognizes the trapezoidal-shaped signal from noise.

Stub lengths of no more than 4 in. must be allowed off the mainline interconnection within any connected equipment to minimize reflections due to impedance discontinuities. This dimension does not include the length of the circuit path through the device connector.

# **Signals and Timing**

The MXIbus defines 80 active signals, 60 ground lines, two lines for termination power, and two lines for auxiliary power. Table 3-1 shows the signal groupings for the MXIbus. See Section 2 for the MXIbus connector pin assignment.

| Table | 3-1. | Signal | Groupings |  |

|-------|------|--------|-----------|--|

|       |      |        |           |  |

| Category     | Description               | Signal Name | Lines |

|--------------|---------------------------|-------------|-------|

| Address/Data | Address/Data              | AD<3100>*   | 32    |

|              | Parity                    | PAR*        | 1     |

|              | Address Modifier          | AM<40>*     | 5     |

|              | Convert                   | CONVERT*    | 1     |

|              | Transfer Size             | SIZE*       | 1     |

|              | Read/Write                | WR*         | 1     |

|              | Address Strobe            | AS*         | 1     |

|              | Data Strobe               | DS*         | 1     |

|              | Data Transfer Acknowledge | DTACK*      | 1     |

|              | Bus Error                 | BERR*       | 1     |

| Arbitration  | Bus Busy                  | BUSY*       | 1     |

|              | Bus Request               | BREQ*       | 1     |

|              | Daisy-Chain Grant In      | GIN*        | 1     |

|              | Daisy-Chain Grant Out     | GOUT*       | 1     |

| Interrupt    | Interrupt Request         | IRQ<71>*    | 7     |

| Timing       | Clock                     | CLK10±      | 2     |

|              | Trigger                   | TRG<70>±    | 16    |

| Utility      | System Reset              | SYSRESET*   | 1     |

|              | System Fail               | SYSFAIL*    | 1     |

|              | AC Fail                   | ACFAIL*     | 1     |

|              | Bus Timeout Disable       | BTODIS*     | 1     |

|              | MXIbus System Controller  | MXISC*      | 1     |

|              | MXIbus End Device         | ENDDEV      | 1     |

| Category | Description      | Signal Name | Lines |

|----------|------------------|-------------|-------|

| Power    | Ground           | GND         | 60    |

|          | Terminator Power | TERMPWR     | 2     |

|          | Auxiliary Power  | AUXPWR      | 2     |

Table 3-1.

Signal Groupings (Continued)

When two devices communicate on the MXIbus, one acts as the master and the other acts as the slave. The master originates an operation and the slave terminates the operation. MXIbus devices are able to assume both roles, although a MXIbus device may have master-only capabilities or slave-only capabilities.

# 3.1 Address/Data

The MXIbus provides support for 32 multiplexed address/data lines (AD<31..00>\*). MXIbus devices may use all or only a subset of the available address/data lines to transfer address and data information between devices; however, it is always the responsibility of the MXIbus master to ensure that the address and data width of the transfer matches the capabilities of the slave device. If a transfer is attempted that the addressed slave cannot complete because of data width incompatibilities, the slave may ignore the transfer, or it may terminate the transfer with a bus error acknowledge.

All MXIbus devices shall have even parity generation and detection circuitry. MXIbus devices generate and source parity along with the address and data portions of all MXIbus transfers. The parity signal (PAR\*) shall be in such a state so that, when considered together with the AD<31..00>\* signal lines, there will be an even number of true (low-level) states.

MXIbus masters and slaves shall generate and check parity by considering the condition of *all* 32 AD<31..00>\* lines. This simplifies the implementation of devices with 32-bit MXIbus interfaces because the parity generation and detection circuitry is the same without regard to the size of the address broadcast or data transfer.

Notice that, although masters and slaves are not required to drive and/or monitor the AD<31..00>\* lines that do not carry valid addressing/data information, a device is permitted to drive the unused lines to simplify the hardware implementation. If unused lines are driven, they shall be driven in a manner consistent with the timing requirements of the lines

that carry valid addressing/data information. If unused lines are not driven, parity compatibility will be maintained considering that all undriven data lines will float to a high level (logical 0) because of the terminators at the ends of MXIbus.

Although it is possible to implement devices with 16-bit or 24-bit MXIbus interfaces, the system integrator must take care to ensure that both the master and slave are compatible with the desired transfer type. For example, a slave device with a 16-bit MXIbus interface must ensure that a 32-bit master generates a parity level that is consistent with the 16 low-order address/data lines. This is assured if the master either always asserts an even number of the unused address/data lines or does not drive any of the unused lines during the transfer, in which case the lines will float to an inactive state. In either case, the parity level will not be affected because an even number of the unused address/data lines will always be either asserted or unasserted. A data read from a slave device with a 16-bit MXIbus interface will always produce the correct parity because the unused address/data lines will float to their inactive state.

### 3.1.1 Address Broadcast

All MXIbus transfers are initiated by an address broadcast cycle in which the current MXIbus master broadcasts the necessary addressing information for the upcoming data cycle to the MXIbus slave(s). This information is provided by the address lines AD<31..00>\*, the address modifier lines (AM<4..0>\*), and the convert (CONVERT\*), transfer size (SIZE\*), read/write (WR\*), and PAR\* signals. The MXIbus slaves latch and/or decode these lines when the address strobe (AS\*) signal becomes asserted to determine how to respond to the following data cycle(s). Only one slave shall respond at a time to each data cycle.

### 3.1.1.1 Address Lines

The MXIbus provides 32 address lines (AD<31..00>\*). These lines are multiplexed with the MXIbus data lines and are latched and/or decoded by the MXIbus slaves on the assertion edge of AS\*. MXIbus masters drive valid address information onto 32, 24, or 16 of the address lines for any given cycle, depending on the address modifier code (see Section 3.1.1.2). Likewise, slaves monitor and decode 32, 24, or 16 of the address lines, depending on the address modifier code. Devices that support 32-bit addresses are called A32 devices. Devices that support 24-bit addresses are called A24 devices, and use address lines AD<23..00>\*. Devices that support 16-bit addresses are called A16 devices, and use address lines AD<15..00>\*. A24 and A16 devices are

not required to monitor, decode, or drive the unused address lines. MXIbus devices can support one or more of the different address spaces.

The MXIbus master device generates the PAR\* signal during the address phase of all transfers. A MXIbus slave that detects invalid parity during any address phase should ignore the transfer and let the bus timeout unit terminate the transfer.

### 3.1.1.2 Address Modifier Lines

In addition to the 32 AD<31..00>\* signal lines, the MXIbus also has five address modifier lines (AM<4..0>\*). These lines are similar in function and meaning to the address modifier lines specified in the IEEE-1014 (or VMEbus) specification, and are used by the MXIbus master to pass additional information (that is, the type of bus cycle being performed) to the slave during a transfer. The address modifier codes are shown in Table 3-2. The *Value* column represents the logical value of the address modifier lines in hex rather than the signal levels.

MXIbus slaves shall not respond to reserved address modifier codes. Reserved address modifier codes are for future enhancements. A MXIbus slave may either ignore or terminate (with a BERR\* acknowledge signal) any transfers within its address space that contain nonreserved address modifier codes that the MXIbus slave does not support.

|      | Addres | s Modifi | er Line |      | Value | Function                           |

|------|--------|----------|---------|------|-------|------------------------------------|

| AM4* | AM3*   | AM2*     | AM1*    | AM0* | (hex) |                                    |

| L    | L      | L        | L       | L    | 1F    | A24, supervisory, block transfer   |

| L    | L      | L        | L       | Н    | 1E    | A24, supervisory, program access   |

| L    | L      | L        | Н       | L    | 1D    | A24, supervisory, data access      |

| L    | L      | L        | Н       | Н    | 1C    | A24, supervisory, D64 transfer     |

| L    | L      | Н        | L       | L    | 1B    | A24, nonprivileged, block transfer |

| L    | L      | Н        | L       | Н    | 1A    | A24, nonprivileged, program access |

| L    | L      | Н        | Н       | L    | 19    | A24, nonprivileged, data access    |

| L    | L      | Н        | Н       | Н    | 18    | A24, nonprivileged, D64 transfer   |

| L    | Н      | L        | L       | L    | 17    | A24, synchronous-burst transfer    |

| L    | Н      | L        | L       | Н    | 16    | Reserved                           |

| L    | Н      | L        | Н       | L    | 15    | A16, supervisory access            |

| L    | Н      | L        | Н       | Н    | 14    | A32, synchronous-burst transfer    |

| L    | Н      | Н        | L       | L    | 13    | Reserved                           |

| L    | Н      | Н        | L       | Н    | 12    | Priority-selection cycle           |

| L    | Н      | Н        | Н       | L    | 11    | A16, nonprivileged access          |

| L    | Н      | Н        | Н       | Н    | 10    | Reserved                           |

| Н    | L      | L        | L       | L    | 0F    | User-defined                       |

| Н    | L      | L        | L       | Н    | 0E    | User-defined                       |

| Н    | L      | L        | Н       | L    | 0D    | User-defined                       |

| Н    | L      | L        | Н       | Н    | 0C    | User-defined                       |

| Н    | L      | Н        | L       | L    | 0B    | User-defined                       |

| Н    | L      | Н        | L       | Н    | 0A    | User-defined                       |

| Н    | L      | Н        | Н       | L    | 09    | User-defined                       |

| Н    | L      | Н        | Н       | Н    | 08    | User-defined                       |

| Н    | Н      | L        | L       | L    | 07    | A32, supervisory, block transfer   |

| Н    | Н      | L        | L       | Н    | 06    | A32, supervisory, program access   |

| Н    | Н      | L        | Н       | L    | 05    | A32, supervisory, data access      |

| Н    | Н      | L        | Н       | Н    | 04    | A32, supervisory, D64 transfer     |

| Н    | Н      | Н        | L       | L    | 03    | A32, nonprivileged, block transfer |

| Н    | Н      | Н        | L       | Н    | 02    | A32, nonprivileged, program access |

| Н    | Н      | Н        | Н       | L    | 01    | A32, nonprivileged, data access    |

| Н    | Н      | Н        | Н       | Н    | 00    | A32, nonprivileged, D64 transfer   |

Table 3-2.

Address Modifier Codes

Block transfer address modifier codes indicate that MXIbus block-mode data is being transferred. For more information about block transfers, refer to Section 3.1.2.2.

D64 transfer address modifier codes indicate that 64-bit data is being transferred over the MXIbus. Since the MXIbus is a 32-bit bus, two 32-bit data transfers are used for each 64-bit data to be transferred. The signaling and timing for D64 transfers over the MXIbus is identical to that of 32-bit block cycles described in Section 3.1.2.2, but with two restrictions. The first restriction is that the block must begin on an 8-byte boundary (address lines 2, 1, and 0 all logical 0). The other restriction is that an even number of 32-bit words must be transferred because each pair of 32-bit words gets combined into a single 64-bit data word at the destination.

Synchronous-burst address modifier codes indicate that MXIbus synchronous-burst data is being transferred. For more information about synchronous-burst transfers, refer to Section 3.1.2.3.

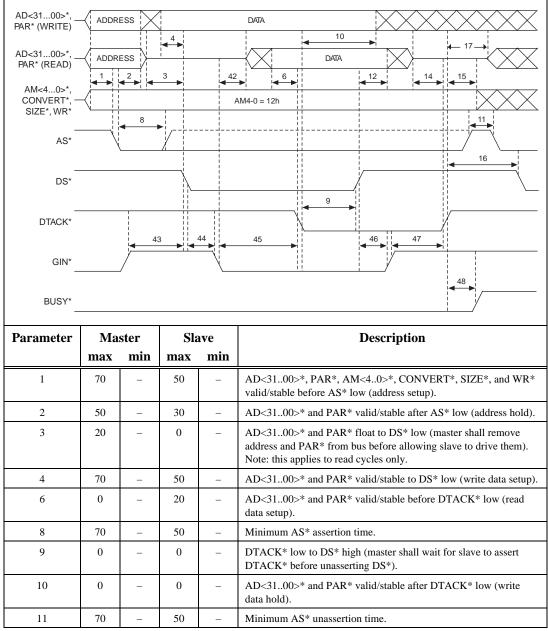

A MXIbus master can use the priority-selection cycle address modifier code (a logical value of AM < 4..0 > \* = 12 hex) to qualify multiple MXIbus slaves so that only the highest priority slave is selected during the data cycle. For more information on this technique, see Section 3.1.2.5.

User-defined address modifier codes are available for any purpose that MXIbus vendors or users deem appropriate.

### 3.1.1.3 CONVERT\* Line

The MXIbus defines a data transfer conversion signal (CONVERT\*). When this signal is asserted during a block or indivisible transfer (for information regarding block and indivisible transfers, see Sections 3.1.2.2 and 3.1.2.4 respectively), the MXIbus interface on the slave device must convert the block or indivisible cycles into single accesses on the slave's local bus. This conversion can increase performance to devices that do not support block or indivisible transfers on the local bus because block or indivisible transfers can still go across the MXIbus. When a MXIbus slave is converting a block cycle, the address of the single local accesses should be incremented by the data width for each access (4 for 32-bit blocks, 2 for 16-bit blocks, and 1 for 8-bit blocks) to access locations in ascending order. The address of the single cycles on the local bus should remain constant when converting indivisible cycles.

### 3.1.1.4 WR\* Line

The MXIbus read/write signal (WR\*) controls the direction of data flow during data transfers. When WR\* is low, the MXIbus master performs a write cycle and supplies the data for the slave to store. When WR\* is high, the MXIbus master performs a read cycle and the slave provides the data to the master.

### 3.1.2 Data Transfers

The MXIbus has 32 data lines (AD<31..00>\*). These lines are multiplexed with the MXIbus address lines, and data is transferred while the data strobe (DS\*) signal is asserted. The MXIbus supports 8-bit, 16-bit and 32-bit data transfers by encoding the transfer size on the AD01\*, AD00\*, and SIZE\* lines (refer to Table 3-4). Data transfers that use all 32 data lines are called D32 cycles. Transfers that use 16 or 8 bits of the data bus are called D16 or D08 cycles, respectively, and use data lines AD<15..00>\*. MXIbus devices can support one or more of the different data sizes.

The smallest addressable unit of storage is the byte location. Each byte may be assigned to one of four categories, according to the value of the least significant two bits of its address, as shown in Table 3-3. The *Byte Address* shown in the table represents the logical value rather than the signal levels.

| Category | Byte Address (AD<3100>*) |

|----------|--------------------------|

| Byte(0)  | <i>XXXXXX</i> 00b        |

| Byte(1)  | <i>XXXXXX</i> 01b        |

| Byte(2)  | XXXXXX10b                |

| Byte(3)  | <i>XXXXXX</i> 11b        |

Table 3-3. Byte Addressing

A set of four bytes whose address differs only in the two least significant bits is referred to as a *longword*. Some, or all, of the bytes in a longword may be accessed simultaneously by a single MXIbus cycle. MXIbus masters use address lines AD < 31..02 > \* and the address modifier lines AM < 4..0 > \* to select which longword will be accessed. Three additional lines,  $AD01^*$ ,  $AD00^*$ , and SIZE\*, select which byte location(s) within the longword are accessed during the data transfer, as shown in Table 3-4.

| Transfer             | SIZE*  | Address Phase |        | Data Phase |           |                    |                    |

|----------------------|--------|---------------|--------|------------|-----------|--------------------|--------------------|

| Size                 |        | AD01*         | AD00*  | AD<3124>*  | AD<2316>* | AD<1508>*          | AD<0700>*          |

| 8-bit<br>(Byte)      | H<br>H | H<br>H        | H<br>L |            |           | Byte(0)            | Byte(1)            |

|                      | H<br>H | L<br>L        | H<br>L |            |           | Byte(2)            | Byte(3)            |

| 16-bit<br>(Word)     | L<br>L | H<br>L        | H<br>H |            |           | Byte(0)<br>Byte(2) | Byte(1)<br>Byte(3) |

| 32-bit<br>(Longword) | L      | Х             | L      | Byte(0)    | Byte(1)   | Byte(2)            | Byte(3)            |

Table 3-4. Data Transfer Types

Depending on how they are mapped in MXIbus address space, 8-bit-only devices can be designed to always transfer data on *either* AD<15..08>\* *or* AD<07..00>\*, or they can be designed to transfer data on *both* AD<15..08>\* *and* AD<07..00>\*. Of course, 16-bit devices shall be able to drive/receive data lines AD<15..00>\*, and 32-bit devices shall be able to drive/receive all 32 data lines. All MXIbus devices, regardless of how they represent data on their internal local buses, shall be responsible for ensuring that all data transfers take place over the proper MXIbus data lines.

It is recommended that D16 devices also support D08 transfers if their local bus supports 8-bit transfers. Similarly, it is recommended that D32 devices also support D16 and D08 transfers, as long as their local buses support the smaller width transfers.

During a write cycle, the MXIbus master asserts DS\* to indicate that it has placed valid data and valid parity driven on the PAR\* signal on the bus. The addressed MXIbus slave asserts data transfer acknowledge (DTACK\*) to indicate that it has successfully received the data.

During a read cycle, the addressed MXIbus slave asserts DTACK\* to indicate that it has successfully placed valid data and valid parity driven on the PAR\* signal on the bus. The MXIbus master unasserts DS\* when it receives the data.

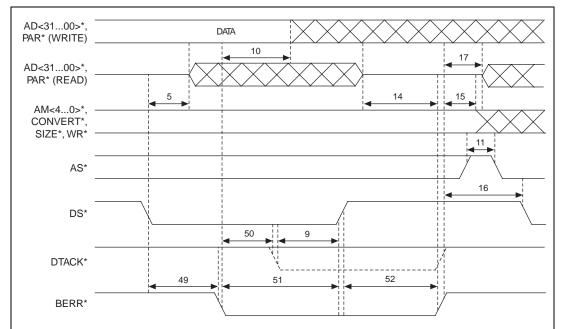

The addressed slave may optionally terminate a MXIbus cycle with a RETRY or BERR\* response rather than the DTACK\* response to DS\* from the master. The slave uses the RETRY response if it is currently unable to complete the transfer but would be able to at a later time. If the slave terminates the transfer with a BERR\* response, the data transfer is

considered invalid and the cycle is prematurely terminated. The signal timing relationships for the RETRY and BERR\* response are slightly different than the DTACK\* response. For more information on the RETRY and BERR\* response, see Section 3.1.2.6.

The MXIbus supports five fundamental types of data transfers:

- Basic

- Block

- Synchronous burst

- Indivisible

- Priority select

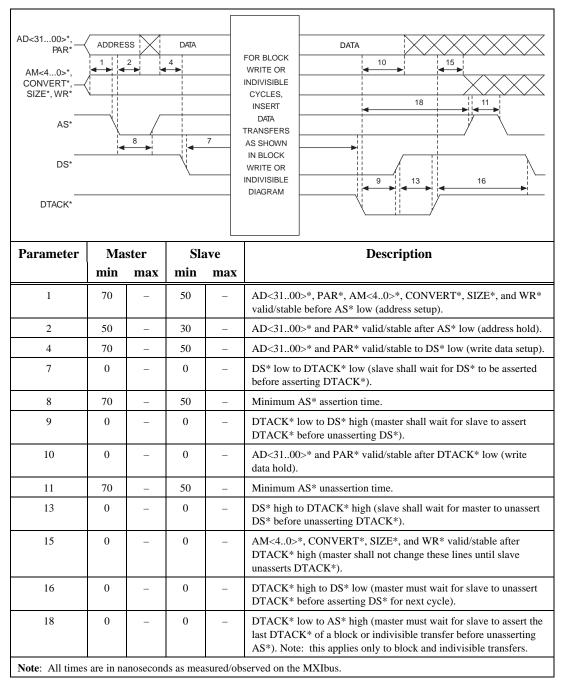

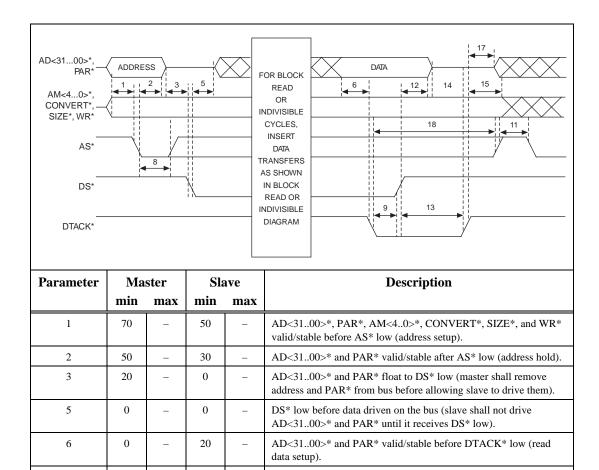

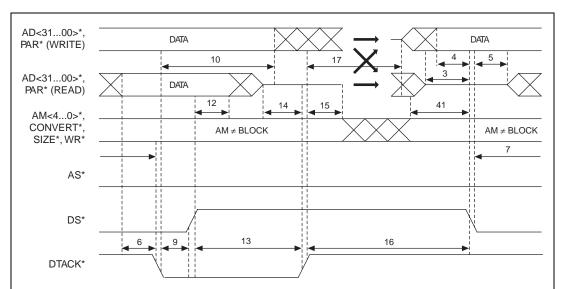

Section 3.1.2.1 describes the basic data transfers, while Figures 3-1 and 3-2 show the timing requirements for basic write and read data transfers, respectively. Section 3.1.2.2 explains block transfers, and the block timing diagrams are presented in Figures 3-3 and 3-4. Synchronous-burst cycle timing is shown in Figures 3-5 through 3-12, and is explained in Section 3.1.2.3. Indivisible cycle timing is shown in Figure 3-13, and is explained in Section 3.1.2.4. Priority-selection cycles are shown in Figure 3-14 and described in Section 3.1.2.5.

Section 3.1.2.6, which describes the RETRY and BERR\* acknowledgments, applies to most types of MXIbus data transfer cycles. Figure 3-15 shows the timing of a slave with a RETRY or BERR\* acknowledgment in response to any of the allowed MXIbus data transfer cycles.

Notice that in these timing diagrams, *master* refers to the timing as seen on the MXIbus at the master device connector; *slave* refers to the timing as seen on the MXIbus at the slave device connector.

### 3.1.2.1 Basic Data Transfers

During a basic transfer cycle, the master broadcasts an address and a single data transfer takes place between the master and the addressed slave. This is the most basic type of data transfer on which all other transfer types are based. The basic data transfer cycle address modifier codes are shown in Table 3-5. The table shows the address modifier logical values in hex rather than the signal levels.

| Address Modifier<br>AM<40>* | Description                        |

|-----------------------------|------------------------------------|

| 1E                          | A24, supervisory, program access   |

| 1D                          | A24, supervisory, data access      |

| 1A                          | A24, nonprivileged, program access |

| 19                          | A24, nonprivileged, data access    |

| 15                          | A16, supervisory access            |

| 11                          | A16, nonprivileged access          |

| 06                          | A32, supervisory, program access   |

| 05                          | A32, supervisory, data access      |

| 02                          | A32, nonprivileged, program access |

| 01                          | A32, nonprivileged, data access    |

Table 3-5. Basic Data Transfer Cycle Address Modifier Codes

The MXIbus master device generates the PAR\* signal during the data phase of basic write transfers. A MXIbus slave that detects invalid parity during the data phase of a basic write transfer should either respond with a BERR\* or ignore the transfer and let the bus timeout unit terminate the transfer.

Figure 3-1. Basic Write Cycle Timing

The MXIbus slave device generates the PAR\* signal during the data phase of basic read transfers. A MXIbus master that detects invalid parity during the data phase of a basic read transfer should treat the data received as corrupt and handle the error appropriately.

| Figure 3-2.  | Basic Read Cycle Timing  |

|--------------|--------------------------|

| 11gui 0 0 21 | Baolo Hoad Oyolo Hilling |

hold).

Minimum AS\* assertion time.

DTACK\* before unasserting DS\*).

DS\* before unasserting DTACK\*).

Minimum AS\* unassertion time.

DTACK\* low to DS\* high (master shall wait for slave to assert

AD<31..00>\* and PAR\* valid/stable after DS\* high (read data

DS\* high to DTACK\* high (slave shall wait for master to unassert

70

0

70

0

0

\_

\_

\_

\_

8

11

12

13

50

0

50

0

0

\_

\_

\_

| Parameter | Master |         | Slave |     | Description                                                                                                                                                                                          |

|-----------|--------|---------|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | min    | min max |       | max |                                                                                                                                                                                                      |

| 14        | 0      | -       | 20    | -   | AD<3100>* and PAR* float before DTACK* high (slave shall quit driving AD<3100>* and PAR* before unasserting DTACK*).                                                                                 |

| 15        | 0      | _       | 0     | -   | AM<40>*, CONVERT*, SIZE*, and WR* valid/stable after<br>DTACK* high (master shall not change these lines until slave<br>unasserts DTACK*).                                                           |

| 17        | 0      | _       | 0     | -   | DTACK* high to AD<3100>* and PAR* driven by master<br>(master shall wait for slave to unassert DTACK* before driving<br>AD<3100>* and PAR*).                                                         |

| 18        | 0      | _       | 0     | _   | DTACK* low to AS* high (master must wait for slave to assert the last DTACK* of a block or indivisible transfer before unasserting AS*). Note: this applies only to block and indivisible transfers. |

Figure 3-2. Basic Read Cycle Timing (Continued)

### 3.1.2.2 Block Transfers

Masters often access memory locations in ascending order. When this is the case, block transfer cycles can be beneficial because they allow the MXIbus master to provide a single address, and then access data in that location and those at higher addresses, without providing additional addressing information. MXIbus devices are not required to implement block-mode functionality, but it is recommended that they do, because block-mode transfers can result in significant improvements in performance. A MXIbus master initiates block-mode operation by sourcing one of the address modifier codes shown in Table 3-6. The table shows the address modifier logical values in hex rather than the signal levels.

| Address Modifier<br>AM<40>* | Description                        |

|-----------------------------|------------------------------------|

| 1F                          | A24, supervisory, block transfer   |

| 1C                          | A24, supervisory, D64 transfer     |

| 1B                          | A24, nonprivileged, block transfer |

| 18                          | A24, nonprivileged, D64 transfer   |

| 07                          | A32, supervisory, block transfer   |

| 04                          | A32, supervisory, D64 transfer     |

| 03                          | A32, nonprivileged, block transfer |

| 00                          | A32, nonprivileged, D64 transfer   |

Table 3-6. Block Transfer Address Modifier Codes

When a MXIbus master initiates a block transfer cycle, all of the MXIbus block-mode slaves on the bus latch the MXIbus address into onboard address counters and examine the address (and the address modifier code) to determine if the address is within their address ranges. The block-mode slave that is selected then participates in the data transfer. All MXIbus block-mode slaves shall increment their address counters by the width of the data (4 for 32-bit block, 2 for 16-bit block, and 1 for 8-bit block) at the end of each data transfer within the block and examine the resulting address to determine if the next cycle is intended for them. The MXIbus slave that is selected then participates in the next cycle.

The MXIbus master, upon completing the first data transfer, shall not unassert AS\* as it would for a normal cycle. Instead, it shall continue to assert AS\* for the duration of the block transfer, and shall repeatedly assert and unassert DS\* in response to DTACK\* acknowledgments from the addressed MXIbus slave, and thereby transfer data to or from sequential address locations in ascending order. To access the next location(s) on their local buses, the block-mode slaves can either source the new value of the address counter on the local bus, or, if possible, perform block-mode transfers on their local buses.

Notice that the length of a block transfer is not limited to the address space of a single MXIbus device, because each MXIbus block-mode slave shall continually monitor and decode the output of its onboard address counter. The length of a block-mode transfer may range from one transfer (4, 2, or 1 B, depending on the width of the data path) up to 4 GB (for A32 space).

The MXIbus master shall hold AS\* asserted until the responding slave asserts DTACK\* for the last transfer of the block-mode operation. The unassertion of AS\* indicates the end of the block-mode transfer. The slave can use this signal to release control of its local bus, or to perform any other device-dependent function.

During D64 mode (address modifier codes hex 1C, 18, 04, and 00), every two sequential data transfers on the MXIbus are considered a single 64-bit datum by the slave because the MXIbus has only 32 data lines.

MXIbus devices that are transferring data in 8-bit (byte) blocks shall alternate the byte lane used to carry data for each cycle throughout the block-mode operation. The byte lane that is used for any given cycle depends on the implicit state of the two least significant address lines, as shown in Table 3-4.

The MXIbus master is responsible for ensuring that block-mode operations are initiated only with slave devices that support block-mode operation. If a block-mode operation is attempted with a slave that does not support block-mode, the slave may ignore the cycle, or it may immediately terminate the transfer with a BERR\* response.

The MXIbus master device generates the PAR\* signal during each data phase of a block-write transfer. A MXIbus slave that detects invalid parity during a data phase of a block-write transfer should either respond with a BERR\* or ignore the transfer and let the bus timeout unit terminate the transfer.

| 70 | _         | 50                       | _                                                     | AD<3100>* and PAR* valid/stable to DS* low (write data setup).                                              |

|----|-----------|--------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 0  | -         | 0                        | -                                                     | DS* low to DTACK* low (slave shall wait for DS* to be asserted before asserting DTACK*).                    |

| 0  | -         | 0                        | -                                                     | DTACK* low to DS* high (master shall wait for slave to assert DTACK* before unasserting DS*).               |

| 0  | -         | 0                        | -                                                     | AD<3100>* and PAR* valid/stable after DTACK* low (write data hold).                                         |

| 0  | -         | 0                        | -                                                     | DS* high to DTACK* high (slave shall wait for master to unassert DS* before unasserting DTACK*).            |